Open loop 최소화 하기

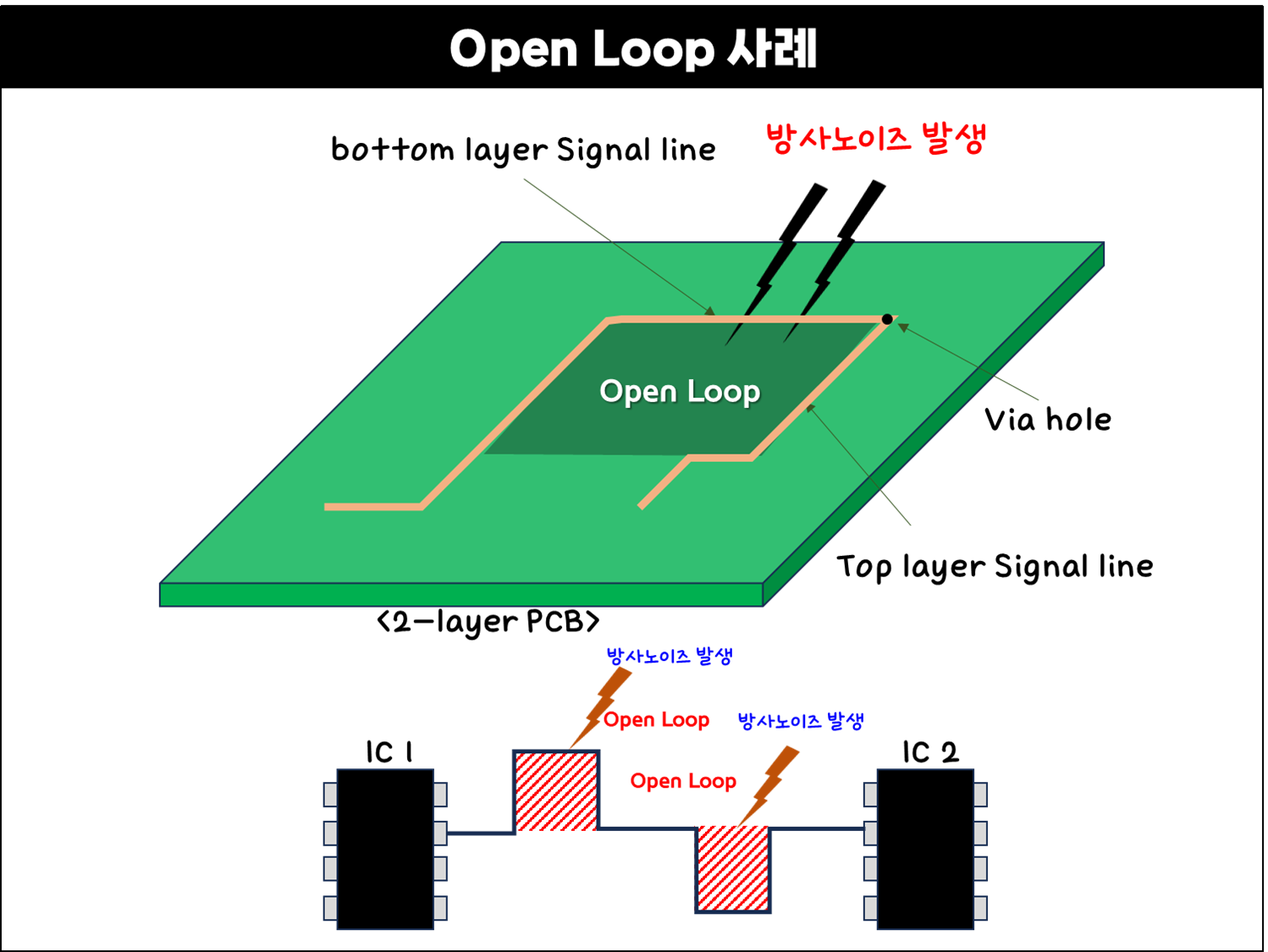

open loop는 아래의 그림과 같습니다. Signal line을 그리다 보면 아래와 같이 open loop가 발생합니다. 어쩔 수 없이 발생하는 경우도 있지만 대부분 생각 없이 설계를 하다 보면 이런 실수를 하게 됩니다.

open loop발생시 문제점과 설계시 check사항

- Signal line이 Clock 배선이거나 고속신호 배선일 경우 open loop는 방사 노이즈를 증가시킵니다.

- 방사노이즈의 발생원인과 문제점에 대해서는 이전 포스팅에서 상세하게 설명드린 적이 있습니다. 기억이 나지 않으면 이전 글을 참조해 주세요.

- open loop의 면적이 크면 클수록 방사노이즈도 커집니다.

- 설계를 하다보면 어쩔 수 없이 open loop가 발생한다고 하더라도 Open loop의 면적을 최소화 하는 방향으로 설계해야 합니다.

Open loop 대책

- 대책은 단순합니다. open loop가 발생하지 않도록 설계하면 됩니다.

- 하지만 말이 쉽죠. 한정된 PCB사이즈에 설계를 하다 보면 open loop는 발생할 수 밖에 없습니다.

- PCB설계를 하시는 분들은 다들 잘 아시겠지만 signal line은 최단거리 설계가 기본입니다. 최단거리 설계를 했음에도 open loop가 발생한다면 그건 어쩔 수 없습니다.

- 정리해 보면 1) open loop가 생기지 않도록 signal line을 배선한다. 2) 어쩔수 없이 open loop가 생길 수 밖에 없는 상황이라면 가능한 open loop의 면적을 최소화 한다.

고찰

1층이나 2층 PCB를 설계할 때는 쉽게 open loop를 발견할 수 있고 해결하기도 수월합니다. 하지만 회로가 복잡해지고 핀수가 많은 마이컴을 설계하다보면 PCB의 층수가 늘어나게 되고 배선이 복잡해 지면서 필연적으로 나올 수 밖에 없는게 open loop입니다. 이를 최소화 하기 위해서는 가장 먼저 부품 레이아웃을 어떻게 하느냐에 달려 있습니다. 최대한 배선을 짧게 가져갈 수 있도록 부품 레이아웃이 최적화 되어야 합니다. 그리고 나서 고속 주파수를 사용하는 signal line을 우선순위로 배선해 나가야 합니다. 그럼에도 불구하고 발생하는 open loop는 어쩔 수 없는 거겠죠. 100% 완벽한 설계는 없습니다. 가장 중요한 것 평가사양을 인지하고 평가시 NG가 발생하지 않도록 잘 조정해 가면서 설계해 나가는 것이 BEST입니다.